NXP Expands Embedded Vision Portfolio with i.MX 952

2 Min Read February 25, 2026

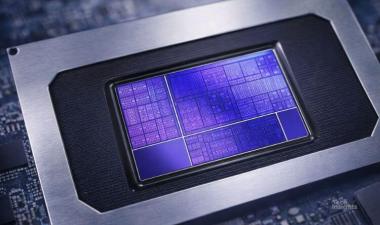

Microprocessor report on NXP’s i.MX 952, which features an eIQ Neutron NPU, quad Cortex-A55 application cluster, and a real-time Cortex-M7.

NXP’s i.MX 952 targets cabin sensing applications that require predictable timing, functional safety, and compute resources. The SoC comprises a quad Cortex-A55 application cluster, a real-time Cortex-M7, and an isolated Cortex-M33 safety core, which collectively keep high-level decision logic, control loops, and supervisory functions from interfering with one another. Domain separation gives system designers clearer control over jitter, latency, and safety behavior when operating control workloads and CNN inference in parallel. To support these workloads, the i.MX 952 integrates an eIQ Neutron NPU for inference, an Arm Mali-T GPU for 2D and 3D human-machine interface rendering, MIPI-CSI capture for direct sensor ingress, and a hardware local-dimming engine for deterministic display behavior. The device is paired with a 32-bit LPDDR5/LPDDR4X memory interface and a wide peripheral set that includes dual Ethernet, CAN-FD, PCIe, and multiple serial controllers.

This summary outlines the analysis* found on the TechInsights' Platform.

*Some analyses may only be available with a paid subscription.