Logic Webinar

Fan-Out Packaging Technologies - The Past and Future

TSMC, Apple, and Samsung have all leveraged different Fan-Out Packaging. Join us to get an update on the latest progress of Wafer Level and Panel Level Fan-Out Packaging.

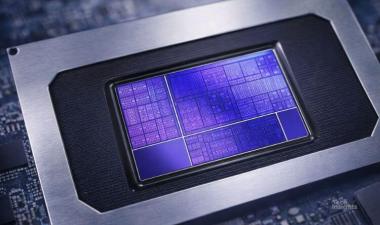

Low-density Fan-Out packaging technology has been around for more than a decade. Due to limitations in RDL counts and line space/line width capabilities, this technology has traditionally been used in low-to-medium pin count applications, such as Power Management ICs (PMIC), audio codecs and RF devices.

TSMC was the first to introduce a high-density wafer-based fan-out package technology solution called Integrated Fan-Out (InFO). This technology targets higher pin count applications, such as application processors (AP). Apple was an early adopter of this new technology, first used in the A10 application processor of the iPhone 7, introduced in late 2016.

Samsung has introduced Fan-Out Panel Level Packaging (FOPLP) technology. FOPLP is a high-density, panel-based Fan-Out package technology which competes directly with TSMC's InFO. In their latest Galaxy smartwatch, Samsung first used the FOPLP to co-package an AP die with a PMIC die.

In this webinar, we'll take a look back at our analysis which reviews the key elements of the two packaging solutions. We'll discuss the following:

- Package cross-sections and RDL delayering images. Understand the structures and the differences between the two technology approaches.

- An update on the latest progress of Wafer Level Fan-Out Packaging and Panel Level Fan-Out Packaging.

- Apple M1 Ultra case study of packaging technology.

- Sneak peek of our next Logic Packaging webinar.

Find content like this and more in the TechInsights Platform. Sign-up for free today.

About the Speakers

Cameron McKnight-MacNeil

Process Analyst

Cameron is a Process Analyst and Packaging Subject Matter Expert at TechInsights, authoring subscription reports on and patent analysis of advanced semiconductor packaging technologies. The devices he regularly analyzes include logic, imaging systems and power-switching devices. Cameron has worked in semiconductor failure analysis and reverse engineering for over ten years, with experience in product development, marketing, and management.

Michel Roy

Senior Process Analysis Engineer

Michel holds the position of Senior Process Analysis Engineer at TechInsights. He provides technical support for patent licensing and patent evaluation based on reverse engineering output, as well as technical structural and material analysis of packages. He has over 25 years of professional experience in the semiconductor packaging industry in package process engineering, package design engineering, package reliability and failure analysis.